Recently Kevin McDermott, Imperas VP Marketing, was invited to share some views for the year ahead

The Lost Art of Microprocessor Verification & Virtual Platforms Announce a Comeback Tour

Microprocessors have been a disruptive force within the electronics industry since the 1970’s, bringing compute resources to new levels of devices and breaking barriers as innovation based on the key specification of ISA (…

How close can we get to automated system optimization from a software function? The target keeps moving but the tools keep becoming more capable

Building an optimal implementation of a system using a functional description has been an industry goal for a long time, but it has proven to be much more difficult than it sounds.

The general idea is to take software designed to run on a processor and to improve performance using various types of alternative hardware.…

Tools and methodologies exist, but who will actually do the verification is unclear.

While the promised flexibility of open source could have advantages and possibilities for processors and SoCs, where does the industry stand on verification approaches and methodologies from here? Single-source ISAs of the past relied on general industry verification technologies and methodologies, but open-source ISA-based processor users and adopters will need to review the verification flows of the processor and SoC.

…

Imperas code morphing simulation technology, virtual platforms and tools used by lead customers for early software development and high-level architectural exploration

Oxford, United Kingdom, December 4th, 2019 — Imperas Software Ltd., the leader in virtual platforms and high-performance software simulation, today announced with Andes Technology Corporation, the close collaboration with lead customers for the latest…

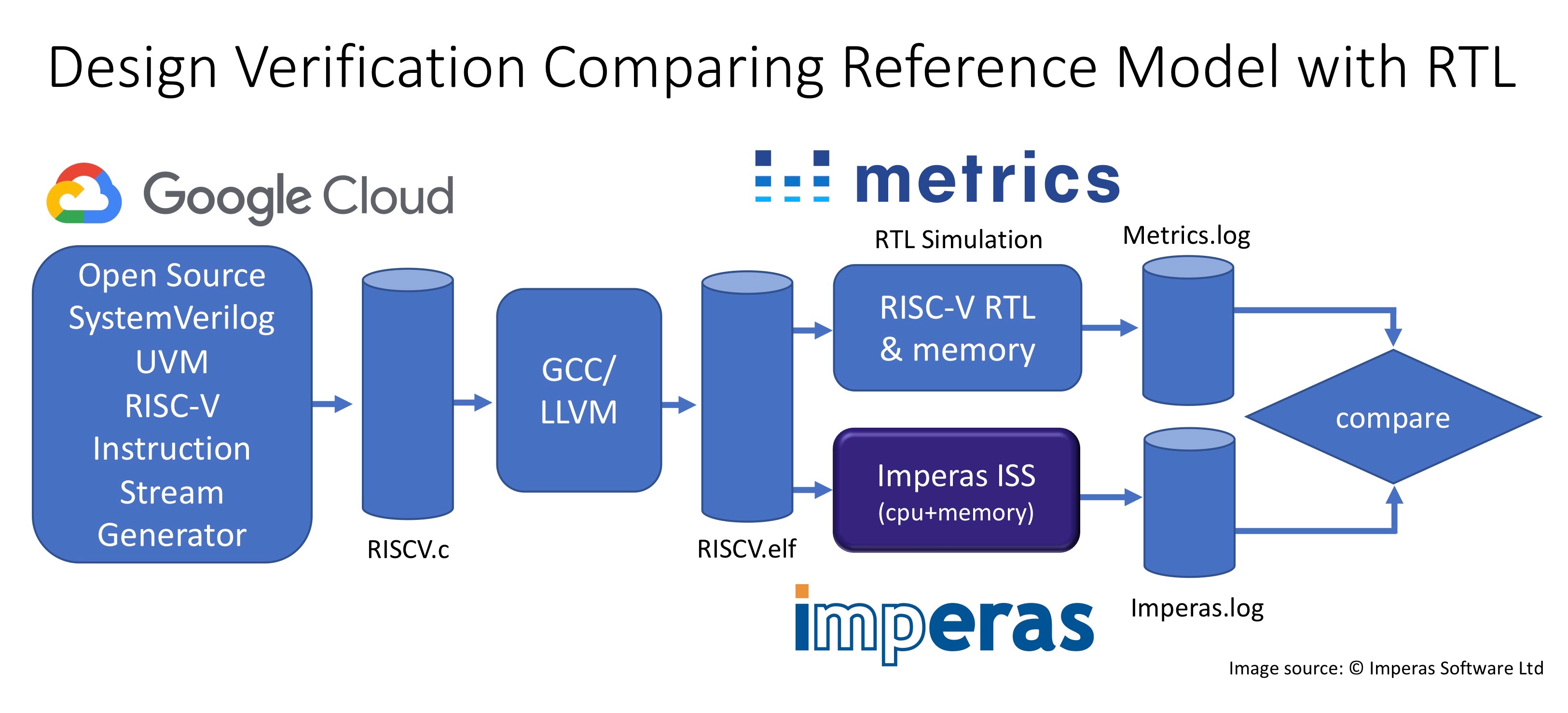

Imperas developed compliance tests quantified by open source collaboration of verification coverage tools developed by Google Cloud

Oxford, United Kingdom, November 26, 2019 — Imperas Software Ltd., the leader in virtual platforms and high-performance software simulation, today announced the release of the latest update to the RISC-V compliance test suite for RV32I base RISC-V configuration. Developed in conjunction with the RISC-V Foundation's Technical Committee task group…

While many companies do have verification plans, demands on those plans are changing faster than most companies can evolve.

Verification plans are rapidly evolving from mechanisms to track verification progress into multi-faceted coordination vehicles for several teams with disparate goals, using complex resource management spread across multiple abstractions and tools.

New system demands from industries such as automotive are forcing tighter integration of those plans with requirements management and product lifecycle development. As a result, today’s verification plan must encapsulate the…

Tutorial to address RISC-V compliance and verification techniques for processor cores including optional custom extensions

Oxford, United Kingdom, October 21, 2019 — Imperas Software Ltd., the leader in virtual platforms and high-performance software simulation, will co-present a tutorial at the 2019 Design and Verification Conference and Exhibition (DVCon Europe) on the latest development in verification and compliance…

Emphasis on flexibility, time to market and heterogeneity requires more processing options.

Open instruction set architectures are starting to gain a foothold, often in combination with other processors, as chipmakers begin to add more specialized compute elements and more flexibility into their designs.

There are a number of these open ISAs available today, including Power, MIPS, and RISC-V, and there are a number of permutations and tools available for sale based on those architectures. What has opened the door to making these more acceptable in designs is that one or more of these…

There may be a second chance for co-design, but the same barriers also may get in the way.

The core concepts in hardware-software co-design are getting another look, nearly two decades after this approach was first introduced and failed to catch on.

What’s different this time around is the growing complexity and an emphasis on architectural improvements, as well as device scaling, particularly for AI/ML applications. Software is a critical component, and the more tightly integrated the software, the better the power and performance. Software also adds an element of flexibility, which is…