At this year’s RISC-V Summit, stakeholders rolled out solutions revolving around verification, security, and software-defined SoCs.

This week is the annual RISC-V Summit in San Jose, CA, where many of the major players in the industry get together to share technology and discuss the future of the RISC-V industry. Building off of the moment of the numerous RISC-V announcements in 2022, this…

These latest models support the NS family of standard processors in safety critical and next-generation embedded systems, for developers using Imperas and other leading EDA tools

Oxford, United Kingdom – December 13th, 2022 – Imperas Software Ltd.,the leader in RISC-V simulation solutions, today announced that NSITEXE, Inc., a group company of the DENSO Corporation that develops processor IP for functional safety and…

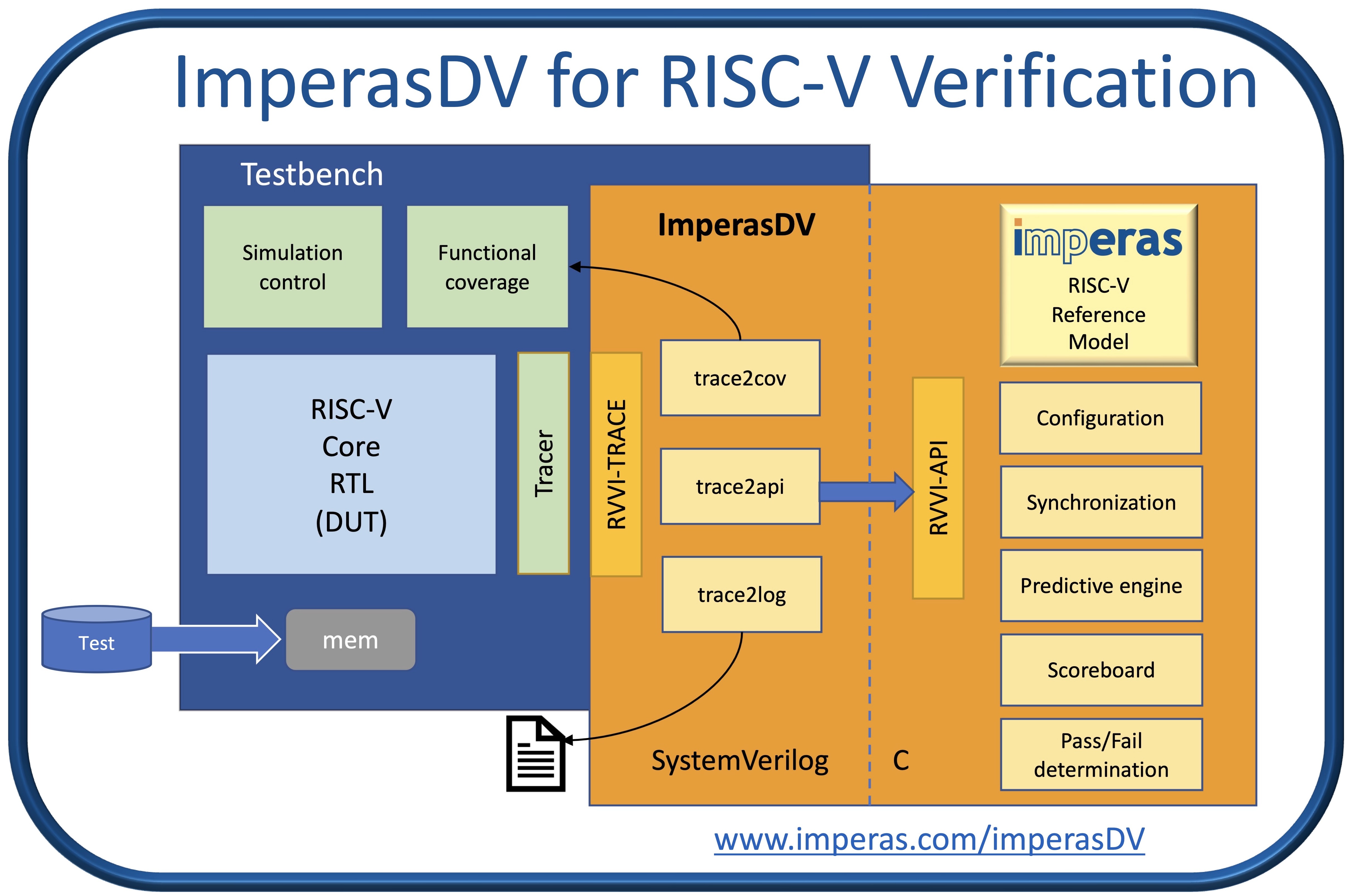

Imperas Software announced the latest updates to ImperasDV to support the rapid growth in RISC-V verification as developers extend into established and emerging applications with new design innovations based on the flexibility of RISC-V. ImperasDV is the integrated solution for RISC-V processor verification that supports both RTL bug detection and analysis, when combined with design flow integration for the leading EDA…

ImperasDV is based on the trusted Imperas reference models and Verification IP, combined with architectural validation test suites and coverage libraries, and with native RVVI support

Oxford, United Kingdom – December 12th, 2022 – Imperas Software Ltd., the leader in RISC-V simulation solutions, today announced the latest updates to ImperasDV to support the rapid growth in RISC-V verification as developers extend into…

Imperas reference model for IMG RTXM-2200 is available on request to lead customers for real-time embedded applications in next generation domain-specific SoCs

Oxford, United Kingdom – December 8th, 2022 – Imperas Software Ltd.,the leader in RISC-V simulation solutions, today announced that Imagination Technologies, a global technology leader in silicon IP (…

Building on 35 years of innovation in RISC processor development, MIPS’ strategic move to RISC-V is supported by Imperas RISC-V Reference Models, Verification IP, and test suites

Oxford, United Kingdom – December 7th, 2022 – Imperas Software Ltd.,the leader in RISC-V simulation solutions, announced today that MIPS, a leading developer of highly scalable RISC processor IP, has selected Imperas to provide advanced RISC-V…

Imperas leadership in the RISC-V Verification Ecosystem recognized in the expanded OpenHW Verification Task Group charter to lead the RISC-V community in adapting to the challenges of RISC-V processor verification

Oxford, United Kingdom – December 5th, 2022 – Imperas Software Ltd., the leader in RISC-V simulation solutions, today announced that Simon Davidmann has been elected as Chair of the OpenHW…

RISC-V intellectual property company Andes Technology has certified simulation reference models from Imperas reference for use evaluating multi-core designs featuring the functional-safety-optimised Andes Core N25F-SE. At the same time, it also certified the complete range of Andes processor IP blocks with ‘Andes Custom Extension’ (ACE) support. Such virtual references run exactly the same binary code as any…

Imperas reference models for Andes expanded with Andes Custom Extension™ support and design flow integration for leading EDA environments, plus new AndesCore® N25F-SE core for functional safety applications

Oxford, United Kingdom – November 29th, 2022 – Imperas Software Ltd., the leader in RISC-V simulation solutions, today announced that Andes Technology Corp., a leading supplier of performance-efficient and extensible 32/64-bit RISC-V processor cores and…