**Imperas Newsletter: June 2017**

# "Silicon without software is just sand."

## **Sketch Cartoon Video Introduction to Imperas**

Fun video on Imperas virtual platforms.

## Watch it here.

RISC-V Gains a Software Development Solution from Imperas

Imperas announced their membership in the RISC-V Foundation, along with Imperas virtual platform and model support for the RISC-V architecture, available now. Imperas demonstrated these embedded software development solutions at the 6th RISC-V Workshop in Shanghai, China in May, and also at the Design Automation Conference (DAC) 2017 in Austin, Texas in June.

- Watch the video. Modern Software

Development Methodology for RISC-V

Devices, here.

- See the RISC-V demo video here.

Recap: Imperas Software @ DAC 2017

We enjoyed meeting all of you who stopped by the Imperas booth @54thDAC 2017 in Austin!

Imperas exhibited our virtual platform solutions, and delivered a virtual platform tutorial: "Linux Bring Up on Heterogeneous Multiprocessor SoCs", with John Min of Imagination Technologies and Simon Davidmann. Read more.

**If you missed DAC**, you can still view Imperas videos and demos online!

- For a rich variety of Imperas videos, across business and technical topics, click here.

- For the virtual platform tutorial: "Linux Bring Up on Heterogeneous Multiprocessor SoCs", contact us.

- For the new video, "Modern Software Development Methodology for RISC-V Devices", <u>click here.</u>

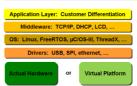

Virtual platforms – software simulation – provide a complementary technology to the current hardwarebased methodology

- Read an article about the RISC-V conference here.

- Read the paper here.

- Read the press release here.

**Agile for Embedded Conference**

Imperas sponsored the May Agile for Embedded Conference in the UK and presented a technical paper on "Target-Based Simulation for Testing of Embedded Software in CI Flows" by Lee Moore, Duncan Graham, Simon Davidmann, and Larry Lapides. Embedded systems have high reliability requirements that demand extensive software testing. Virtual platforms (software simulation) enable the use of unmodified, production binaries, deliver superior controllability, observability and determinism, are easily automated for inclusion in a CI flow, and complement hardware-based testing.

- See the new video, Continuous Integration and Test Automation with Jenkins, here.

- See the conference slides here.

- See the press release here.

New Imperas Virtual Platform Software Delivers

Performance and Models for Automotive, IoT and

Security

Imperas Software announced new software releases of both Imperas and OVP products. These releases focus on enhanced solutions across automotive, IoT, security and other markets, and extending Imperas' leadership in virtual prototyping.

### Highlights include:

- 2x performance improvement in simulation, for fast virtual platform execution to help embedded software developers run more tests in less time.

- New Open Virtual Platforms (OVP)

models for ARM (ARMv8.1), Imagination

Technologies (MIPS I6400), RISC-V (32

bit and 64 bit) and Renesas (RH850)

processors, all popular and widelyadopted in these markets.

- A new iGen modeling productivity tool, for accelerated peripheral and platform development and customization.

#### Read more.

## **OVPsim Release News**

OVP: Fast Simulation, Free open source models, Public APIs: Open Virtual Platforms.

A new Imperas and OVP release became available, May 2017. The <u>Open Virtual Platforms</u> portal is one of the most exciting open source software developments in the embedded software world since GNU created GDB.

For embedded software developers, virtual platforms are increasingly important, especially for multi-core designs.

The resources on this portal can significantly accelerate your development and test. The next release of OVPsim is expected to be available in August 2017.