Past Issues Translate

Imperas Newsletter – Jan. 2023

View this email in your browser

# The leader in RISC-V simulation solutions

Imperas at the RISC-V Summit 2022

As we start the new year, I would like to thank all our customers, partners, and users for a very successful 2022 in which we helped support many RISC-V projects to complete verification and prototype silicon success.

The photo above is of some of our team members, including me, at the RISC-V Summit in San Jose last month. Thanks to everyone that attended the Imperas RISC-V Summit kickoff party, visited our booth, attended our talks, and helped to make the Summit a great event and a perfect conclusion to the year.

I am excited to meet you again in the year ahead.

Kind regards,

Simon Davidmann

President & CEO

Imperas Software Ltd

Imperas releases new updates, test suites, and functional coverage library to support the rapid growth in RISC-V Verification.

For more information, please <u>click here</u>.

## NSITEXE Qualifies Imperas RISC-V Reference Models for Akaria Processors

NSITEXE qualifies Imperas RISC-V reference models for Akaria processors NS72A, NS72VA, and NS31A.

RISC-V Summit 2022 Videos

**Upcoming Events**

## HiPEAC conference, January 16-18 2023

Imperas will participate at the <u>HiPEAC</u> (European Network on High-performance Embedded Architecture and Compilation) conference in Toulouse, France. During the event, Imperas will present a talk on the RISC-V verification ecosystem and also participate in a panel discussion for RISC-V adoption in HPC.

#### Conference talk:

#### New open verification standards for the RISC-V verification ecosystem

Speaker: Jon Taylor – Imperas Software

When: Monday Jan 16 2023: 2:00pm CEST

#### Panel session:

### **European RISC-V in HPC prospective**

Chair: (TBC)

Panelists:

Jon Taylor - Imperas

Roger Espasa - SemiDynamics

Zdenek Prikryl - Codasip Michael Chapman - Cortus

When: Monday Jan 16 2023: 4:45pm CEST

For more information about Imperas's participation during the conference <u>follow</u> <u>this link</u>. To arrange an 1-to-1 appointment during <u>HiPEAC</u>, please email us at: <u>info@imperas.com</u>

## **DVCon, February 27 to March 2 2023**

Imperas will participate at <u>DVCon 2023</u> in San Jose, presenting a joint conference paper with OpenHW, an in-depth tutorial on the latest simulation-based RISC-V processor verification techniques, plus a booth (#108) in the expo hall with the opportunity to <u>chat 1-1 with the Imperas team</u>.

#### Conference paper:

## The Evolution of RISC-V Processor Verification: Open Standards and Verification IP

Co-authors: Aimee Sutton, Imperas Software

Lee Moore, Imperas Software

Mike Thompson, OpenHW Group

When: Tuesday February 28th 3:00pm PST

For more information about Imperas's participation in the event, please <u>follow</u> <u>this link</u>. To arrange an 1-to-1 appointment during <u>DVCon 2023</u>, please email us at: <u>info@imperas.com</u>

## **Embedded World Exhibition and Conference, March 14-16 2023**

Imperas will be at <u>Embedded World 2023</u> in Nuremberg, Germany, demonstrating solutions for RISC-V processor verification, software development with virtual prototypes and extensions with custom instructions in conjunction with debug and analysis tools and solutions to accelerate embedded software development. Imperas are co-sponsors of the RISC-V Pavilion located in Hall 4A stand 4A-620 and will also participate in the following talks:

Conference Paper:

## Advanced methodologies to address RISC-V verification for all adopters

Speaker: Aimee Sutton – Imperas Software Co-authors: Mike Thompson – OpenHW Group

Kevin McDermott – Imperas Software Simon Davidmann – Imperas Software

Lee Moore - Imperas Software

When: Wednesday March 15, 2023: Session 9.2 – 2:15pm

## Conference Paper:

## New ecosystem leads RISC-V mainstream adoption with innovation ready software development and processor verification tools

Speaker: Larry Lapides – Imperas Software

Co-authors: Vijay Krishnan – Intel

Dalton Westergreen – Intel

Mike Thompson – OpenHW Group

Davide Schiavone – OpenHW Group

Kevin McDermott – Imperas Software

Simon Davidmann – Imperas Software

When: Thursday March 16, 2023: Session 9.3 - 12:00pm

## Conference Paper:

## **Example of Extending RISC-V for AI/ML Domain Specific Processors**

Speaker: Larry Lapides – Imperas Software Co-authors: Pascal Gouedo – Dolphin Design

Damien Le Bars – Dolphin Design

Olivier Montfort – Dolphin Design

Mike Thompson – OpenHW Group

Kevin McDermott – Imperas Software

Lee Moore – Imperas Software Aimee Sutton – Imperas Software

When: Thursday March 16, 2023: Session 9.3 - 4:00pm

#### RISC-V Theatre:

#### **Introduction to RISC-V Processor Verification**

Speaker: Larry Lapides – Imperas Software

Co-Authors: Lee Moore - Imperas Software

Aimee Sutton – Imperas Software

When: Tuesday March 14, 2023: TBD

#### **RISC-V Theatre:**

## **Getting started with RISC-V custom instructions**

Speaker: Kevin McDermott – Imperas Software

Co-Author: Duncan Graham - Imperas Software

When: Wednesday March 15, 2023: TBD

Stop by the RISC-V Pavilion (Hall 4A stand 4A-620) to see all the latest Imperas simulation technology for RISC-V, including advanced RISC-V processor verification, virtual prototypes, software development and custom instruction, plus support for the latest ratified RISC-V specifications including vector accelerators and draft extensions included with the Imperas reference model for RISC-V.

For more information, please <u>follow this link</u>, or to set up meetings with Imperas at the <u>Embedded World 2023</u>, please contact: <u>info@imperas.com</u>

**Articles**

### Simulation model certified for functional safety RISC-V core

RISC-V intellectual property company Andes Technology has certified simulation reference models from Imperas reference for use in evaluating multi-core designs featuring the functional-safety-optimised Andes Core N25F-SE. At the same time, it also certified the complete range of Andes processor IP blocks with 'Andes Custom Extension' (ACE) support.

To read the full **Electronics Weekly** article by **Steve Bush**, <u>click here</u>.

## Imperas announces updates to ImperasDV

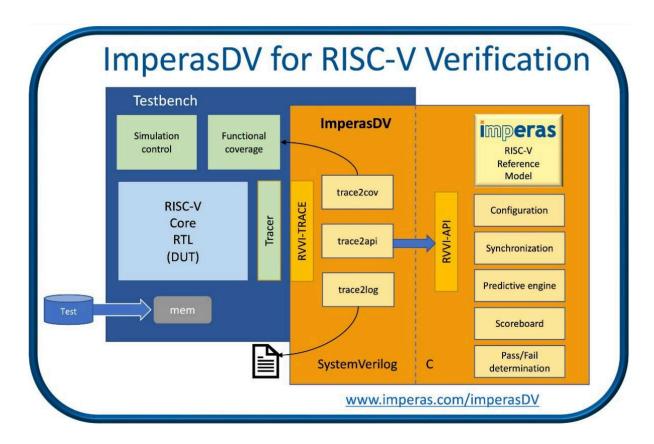

ImperasDV is the integrated solution for RISC-V processor verification that

supports both RTL bug detection and analysis, when combined with design flow integration for the leading EDA SystemVerilog environments with Cadence, Siemens EDA, and Synopsys.

To read the full **Electronic Specifier** article by **Beth Floyd**, <u>click here</u>.

## <u>Imperas Announces Ratifications, Test Suites, and Functional Coverage</u> <u>Libraries for RISC-V</u>

Imperas Software Ltd. revised its ImperasDV for maintaining the expansion of RISC-V verification supporting both RTL bug detection and analysis while collaborating with design flow implementation in EDA SystemVerilog environments with Cadence, Siemens EDA, and Synopsys.

To read the full **Embedded Computing Design** article by **Chad Cox**, <u>click</u> here.

## **Adapting To Broad Shifts Essential In 2022**

Every year holds a number of surprises, and change provides an opportunity to innovate and gain an advantage over those who are slower to adapt.

To read the full **Semiconductor Engineering** article by **Brian Bailey**, <u>click</u> here.

#### **RISC-V Pushes Into The Mainstream**

RISC-V cores are beginning to show up in heterogeneous SoCs and packages, shifting from one-off standalone designs toward mainstream applications where they are used for everything from accelerators and extra processing cores to

security applications.

To read the full Semiconductor Engineering article by Marie Baca and Ed Sperling, click here.

#### **Release Information**

## riscvOVPsim and riscvOVPsimPlus - LATEST NEWS

The latest Imperas and OVP release at the Open Virtual Platforms website.

For an introduction to RISC-V the free single-core envelope model, called riscvOVPsim, is an excellent starting point, which can be configured for all the ratified ISA features and includes support of the latest ratified specifications including Bit Manipulation, Crypto (scalar) and Vectors.

The latest version is available via GitHub here.

The free enhanced **riscvOVPsimPlus**, including many more features including full configurable instruction trace, GDB/Eclipse debug, and memory configuration options, plus the RISC-V Vector and other test suites, is now available on the OVPworld website here.

Has someone forwarded our newsletter to you? Join our mailing list.

**y** Twitter

## This email was sent to << Email Address>>

why did I get this? unsubscribe from this list update subscription preferences

Imperas Software Limited · Imperas Buildings, North Weston · Thame, Oxfordshire OX92HA · United Kingdom