Imperas Newsletter - May 2020

View this email in your browser

# Revolutionizing Embedded Software Development

**E**mail

#### Latest news

Mellanox selects Imperas RISC-V processor reference model for hardware design verification (DV) including custom extensions

First reference model with UVM encapsulation for Imperas RISC-V verification available

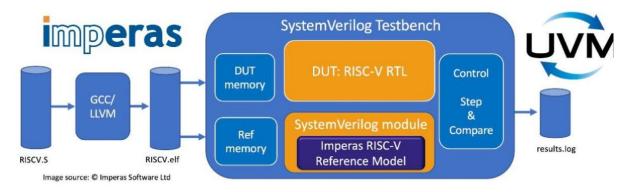

# RISC-V Verification - UVM Step and Compare flow using Imperas Reference Model

- OVP model is encapsulated into SystemVerilog module

- Steps CPUs, extracting data and comparing results

Imperas appoints Coontec as its Certified Design and Verification Partner supporting Leading Edge SoC Designs in South Korea

Imperas CEO Simon Davidmann quoted in the Semiconductor Engineering article by Brian Bailey, 'Why It is So Hard To Create New Processors'.

View the article

The Imperas RISC-V Reference model and verification flow diagram featured in The Register article 'Chips that pass in the night: How risky is RISC-V to Arm, Intel and the others? Very' and was highlighted as "the good news for the RISC-V ecosystem".

See the coverage

**Events**

Join Imperas, Andes, and UltraSoC to learn how to easily customize, accurately simulate, and precisely instrument a multicore RISC-V CPU in an AI inferencing or ML design.

When: May 6<sup>th</sup> 2020 - 8am PDT and 5pm PDT

# Register for today's webinar

## Webinar today

Join Imperas as it presents the key role of virtual platforms in the front end design and architectural exploration phase of a RISC-V based SoC for AI and ML Applications

# Webinar held on Wednesday May 6<sup>th</sup> 2020

With two meeting time slots available to choose from:

Meeting at 8am (PDT) or 5pm (PDT)

## City comparisons:

San Jose: 8am (PDT) or 5pm (PDT)

London: 4pm (BST) or 1am (BST on May 7th)

Paris: 5pm (CET) or 2am (CET on May 7th)

Bangalore: 8:30pm (IST) or 5:30am (IST on May 7th)

Taipei: 11pm (CST) or 8am (CST on May 7th)

## Book your seat:

Register for the webinar

unprecedented times. We hope to restart our regular conference and event activities shortly. Meanwhile, if you would like to schedule a video demo with an application engineer, please email: info@imperas.com. Or view our online tutorials at:

http://www.imperas.com/imperas-resource-library

Request demo

# Other information

## **OVP and riscvOVPsim RELEASE NEWS**

A new Imperas and OVP release became available in November 2019, reference 20191106.0.

The Open Virtual Platform portal is one of the most exciting open-source software developments in the embedded software world since GNU created GDB. For embedded software developers, virtual platforms are increasingly important, especially for multi-core designs.

For an introduction to RISC-V the free single core envelope model, called riscvOVPsim, is an excellent starting point, which can be configured for all the ratified ISA features and includes support of the draft specifications for Bit Manipulation and Vectors. The latest version was uploaded 30 Mar 2020 Version: 20200330.0 and is available at: <a href="https://github.com/riscv/riscv-ovpsim">https://github.com/riscv/riscv-ovpsim</a>

riscvOVPsim, learn more

This email was sent to << Email Address>>

why did I get this? unsubscribe from this list update subscription preferences

Imperas Software Limited · Imperas Buildings, North Weston · Thame, Oxfordshire OX92HA · United Kingdom