Imperas Newsletter October 2019

View this email in your browser

# Revolutionizing Embedded Software Development

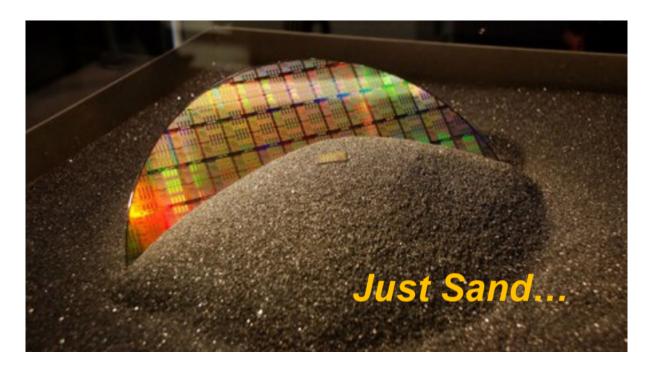

# What's new from Imperas - October 2019 "Silicon without software is just sand."

Welcome to October's edition of our newsletter. It's been a busy couple of months for us at Imperas. In late May we jointly announced with Wave Computing a free to use reference model and simulator for the MIPS OpenTM community of SoC designers and processor architects. MIPSOpenOVPSimTM helps SoC developers by providing a comprehensive testing platform for all MIPS Open specifications and extensions. Read the full details here.

# **RISC-V Specs**

The RISC-V Foundation officially announced the ratification of its base ISA and privileged architecture specifications. we were ready for this and announced our corresponding reference model update to also include the latest drafts for the new Vector and Bit Manipulation extensions, with delivery to leading customers. You can see the full update <a href="here">here</a>.

# **OpenHW**

June was a month for extended collaboration, as a founding supporter of the newly formed OpenHW Group which was

launched on 5th June, again just ahead of the RISC-V workshop in Zurich. This new group will boost the adoption of open-source hardware by providing a platform for collaboration and offering open-source IP for processor cores, starting with the new CORE-V family, you can read about our participation <a href="here">here</a>.

#### **Collaboration with Metrics**

We announced our collaboration with Metrics cloud-based verification platform, to form the basis for a new hardware design verification framework for RISC-V Instruction Stream Generator at the RISC-V Workshop in Zurich. More details available here.

### **Chips Alliance**

The Linux Foundation formally announced Imperas and Metrics as the latest members to join the CHIPS Alliance project, advancing common open hardware interfaces, processors and systems. Our planned contributions will include enhanced interfaces and design flow methodologies to the riscvOVPsim ISS (Instruction Set Simulator) for RISC-V processor IP verification and compliance. More details available here.

These partnerships are all part of our strategy and mission to leverage virtual platform techniques to build revolutionary new solutions for multi-core embedded software development.

For more information on these updates please contact info@imperas.com

#### **EVENTS**

We will participate in the following industry events. Please visit our <u>website</u> for more information or <u>contact</u>

<u>us</u> directly to set up a meeting at any of these events. We look forward to seeing you at:

DVCon Europe 2019 in Munich (October 29-31)

RISC-V Summit 2019 (December 10-12)

Learn More about Imperas products, tools and solutions for Virtual Platforms!

Please email <a href="mailto:info@imperas.com">info@imperas.com</a> to set up meetings with Imperas at any of these events, or for more information about virtual platforms for embedded software and systems development, debug and test. We hope to see you at an upcoming event!

# NEWS - Imperas has been featured in some great industry articles recently:

Brian Bailey in Semiconductor Engineering makes some interesting observation around the possibility of a second chance for co-design, but the same barriers also may get in the way: Semiconductor Engineering: Hardware-Software Co-Design Reappears.

Complex chips require a multitude of verification platforms working in sync and that's where the challenges begin. Which is the opening statement in Ann Mutschler of Semiconductor Engineering interesting article: Semiconductor Engineering: <a href="https://example.com/hybrid/Hybrid/EmulationTakes/Center Stage">Hybrid/Emulation Takes/Center Stage</a>.

UltraSoC invited us to contribute a guest blog following the Cambridge RISC-V Meetup which was at the end of June:

UtraSoC Guest blog: An evening with the RISC-V Community at the Cambridge Meetup.

This interesting article from Brian Bailey in Semiconductor Engineering debates what the understanding of "open source" actually entails: Semiconductor Engineering: <u>Open source Processors: Fact or Fiction?</u>

From the RISC-V Workshop in Zurich Nitlin Dahad of EETimes reported on the latest RISC-V developments and some insights on the new OpenHW group: EETimes: RISC-V Moving Beyond Academia New Group offers Hardened SoCs.

#### **OVP RELEASE NEWS**

OVP: Fast Simulation, Free open source models, Public APIs: Open Virtual Platforms

A new Imperas and OVP release became available in June 2019

The Open Virtual Platform portal is one of the most exciting opensource software developments in the embedded software world

since GNU created GDB.

For embedded software developers, virtual platforms are

increasingly important, especially for multi-core designs.

The resources on this portal can significantly accelerate your development and test. The next release of OVPsim is expected to be available in late October 2019.

Updates include simulator implementation of RISC-V vector specification to align with the latest changes as well as updates to the latest RISC-V Bit Manipulation specification.

Copyright © 2019 Imperas Software Limited, All rights reserved.

<u>Update your preferences</u> or <u>unsubscribe from this list</u>